.

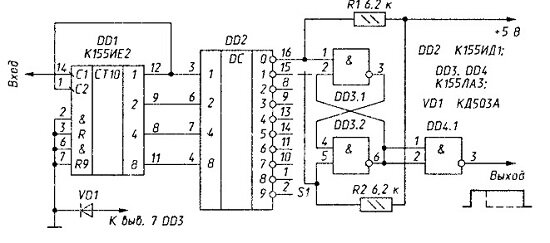

Нередко при построении преобразователей и регуляторов возникает необходимость изменении скважности выходного сигнала. Используя приведенную ниже схему скважность выходного сигнала можно дискретно изменять от 10 до 1.1, причем выходная частота сигнала в 10 раз ниже входного.

На микросхеме DD1 собран счетчик до 10, с его выходов числа от 0 до 9 двоичном коде поступают на двоично-десятичный дешифратор, в качестве которого используется высоковольтный дешифратор К155ИД1. Затем следует обычный RS триггер, который входом Ы всегда подключен к младшему разряду дешифратора, а вход R с помощью галетного переключателя на 9 положений может подключаться в разрядам 1-9.

Таким образом, триггер всегда устанавливается первым импульсом тактового генератора, а сбрасывается вторым – десятым в зависимости от положения переключателя. В результате на выходе устройства появляется сигнал, поделенный на 10 и со скважностью от 10 до 1.1. Поскольку микросхема ИД1 имеет выходы с открытым коллектором, для установки на них высокого уровня (на тех, которые неактивны в данный момент) использованы нагрузочные резисторы R1 и R2, подтягивающие входы триггера к «1», когда ключи дешифратора закрыты.

Еще одна особенность схемы – диод VD1. он необходим для подтяжки уровня срабатывания триггера по «0» до 2 В. Связано это с тем, что высоковольтные ключи микросхемы ИД1 в открытом состоянии выдают ноль, несколько больший (до 1.8 В), чем принят в ТТЛ.

.